tricore architecture - Interrupt System

在 TriCore™ 处理器系统中,多个来源(如外设或外部中断)可以向 中断服务处理单元(如 CPU 或 DMA 通道)发送 中断请求。本章介绍 CPU 的中断处理能力,包括 中断优先级机制 以及 中断向量表的访问。

1 General Operation

每个 中断源 都被分配一个 唯一的中断优先级号,称为 服务请求优先级号(SRPN)。当某个 中断源 发送中断请求时,中断控制单元(ICU) 会使用 SRPN 来决定优先级,并选择最高优先级的请求。

获胜的中断请求 会将其 SRPN 作为“挂起的中断优先级号”(PIPN)发送给 CPU,同时触发中断。CPU 通过比较 PIPN 和 当前 CPU 优先级号(CCPN),决定是否接受该中断:如果 CPU 接受中断,它会发送 中断确认(Interrupt Acknowledge) 并返回被接受的 中断优先级号。ICU 随后会清除该中断源。

1.1 ICU 中断控制寄存器(ICR)

ICU 的中断控制寄存器(ICR) 包含:

- 当前 CPU 优先级号(CCPN)。

- 全局中断使能/禁用位(IE)。

- 当前挂起的中断优先级号(PIPN)。

1.2 CPU 处理中断请求

当 CPU 收到 中断请求 时,它会执行以下检查:

- 检查全局中断使能位(ICR.IE):如果 ICR.IE == 0,则所有中断 都被禁用。

- 比较当前 CPU 优先级(ICR.CCPN)与 PIPN:只有当 PIPN > CCPN 且 ICR.IE == 1 时,CPU 才能被中断。

CPU 可能因以下 情况 无法立即处理中断:

- 全局中断被禁用 (ICR.IE == 0)。

- 当前 CPU 优先级(CCPN)高于或等于挂起的中断优先级号(PIPN)。

- CPU 正在进入中断或陷阱服务程序。

- CPU 正在执行不可被中断的陷阱服务。

- CPU 正在执行多周期指令(如复杂的数学计算)。

- CPU 正在执行修改 ICR 的指令。

CPU 仅在这些条件不再成立时,才会响应新的中断请求。

1.3 进入中断服务例程(ISR)

当 所有阻碍条件被清除后,CPU 进入 中断服务例程(ISR),并执行以下操作:

- 保存当前任务的上层上下文(包括关键寄存器状态)。

- 更新返回地址(A[11]),将当前程序计数器(PC)存入其中。

- 切换到中断栈:如果 CPU 之前未使用中断栈 (PSW.IS == 0),则 A[10](栈指针)被设置为中断栈指针(ISP)。PSW.IS 置为 1,表示当前使用中断栈。

- 进入“监督模式”(Supervisor Mode),开启所有权限:PSW.IO = 10B。

- 保护寄存器集合设置为 0:PSW.PRS = 000B。

- 清除调用深度计数器(Call Depth Counter, CDC) 并设定调用深度限制:PSW.CDC = 0000000B(最大 64 级)。

- 启用调用深度计数器(Call Depth Counter):PSW.CDE = 1

- 设置 PSW 安全位:PSW.S = SYSCON.IS,该位根据 SYSCON 寄存器中定义的值设置,确保进入中断时符合安全机制。

- 禁用对全局寄存器的写入权限:PSW.GW = 0,限制对 A[0], A[1], A[8], A[9] 这四个全局寄存器的写访问。任何中断或陷阱处理程序进入时,默认情况下都无法修改这些寄存器,以保证系统稳定性。

- 禁用全局中断系统:ICR.IE = 0,防止在处理中断时发生新的中断请求。旧的 ICR.IE 值被 保存到 PCXI.PIE,以备恢复。

- 更新 CPU 优先级:ICR.CCPN(当前 CPU 优先级号)存入 PCXI.PCPN(先前 CPU 优先级号)。ICR.PIPN(挂起的中断优先级号)存入 ICR.CCPN,以确保 CPU 在执行 ISR 期间运行于正确的优先级。

- 访问中断向量表,加载 ISR 入口:CPU 计算 ISR 的入口地址,然后跳转执行。

进入 ISR 时,CPU 默认 禁用中断系统 并设置当前优先级。用户可以手动启用中断系统(ICR.IE = 1)。

可以通过 ENABLE 指令来设置ICR.IE = 1,恢复中断处理能力。以及 BISR 指令(Begin Interrupt Service Routine)启用中断系统(会同时更新 ICR.CCPN,并保存被中断任务的下层上下文)。

此外,也允许通过 MTCR指令(Move To Core Register)修改 ICR.IE 或 ICR.CCPN。

ENABLE、BISR 和 DISABLE(禁用中断)指令的执行方式,使得 CPU 在指令完全执行完毕之前不会接受中断请求。这种方式避免了流水线副作用,因此无需在这些指令后执行 ISYNC(同步指令流)。

但 MTCR 是一个例外,必须在其后执行 ISYNC 指令。

2 退出中断服务程序

当 ISR 通过 RFE(从异常返回)指令退出时,硬件会自动恢复上层上下文。上层上下文包括 PCXI 寄存器,该寄存器保存先前的 CPU 优先级编号(PCPN)和先前的全局中断使能位(PIE)。这些位的值被使用如下:

PCXI.PCPN 被写入 ICR.CCPN,以将 CPU 优先级编号恢复到中断前的值。

PCXI.PIE 被写入 ICR.IE,以恢复该位的状态。 随后,被中断的程序继续执行。

3 中断向量表

中断向量表用于将中断服务程序(ISR)与特定优先级的中断关联。

CPU 发生中断时,会根据中断优先级计算出该 ISR 入口,在中断向量表中的位置,并将其加载到程序计数器(PC)中。

随后,CPU 开始执行 ISR 的指令。由于 ISR 代码的大小不同,中断向量表可能只存储 ISR 的初始部分,例如一个跳转指令,以引导 CPU 到完整的 ISR 代码位置。

中断向量表基地址寄存器(BIV) 存储 中断向量表 的基地址。

中断向量在表中按优先级递增排列。BIV 寄存器可以使用 MTCR 指令在系统初始化阶段修改(BIV 受 ENDINIT 保护),在启用中断之前完成修改。借助这种设计,可以使用多个 中断向量表 并通过更改 BIV 寄存器的内容来在它们之间切换。

当发生中断时,CPU 根据优先级 和 BIV 寄存器中内容,来计算对应的中断服务程序(ISR) 入口点。

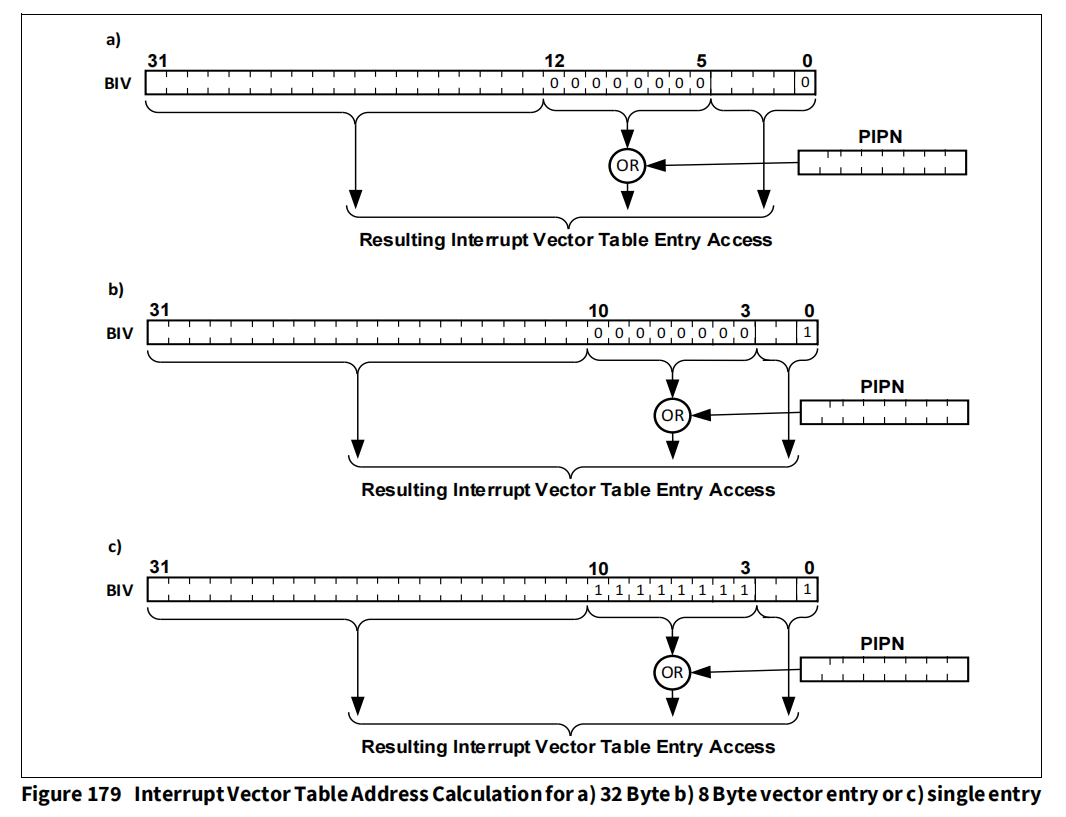

中断向量表 的向量间隔配置有两种,向量间隔可以是 32 字节 或 8 字节,具体间隔由 BIV 寄存器 的 VSS(向量大小选择) 位决定。

要生成指向 中断入口 的指针,PIPN 需左移 5 位(当 VSS=0) 或 3 位(当 VSS=1),然后与 BIV 寄存器的地址 进行 OR 操作 来生成 ISR 入口地址。ISR 的执行从该地址开始。

通过将BIV中参与 OR运算 的位全部置为1,可实现所有 ISR 都进入同一个中断入口,这种方式有利于软件同一管理 ISR。

如下所示:

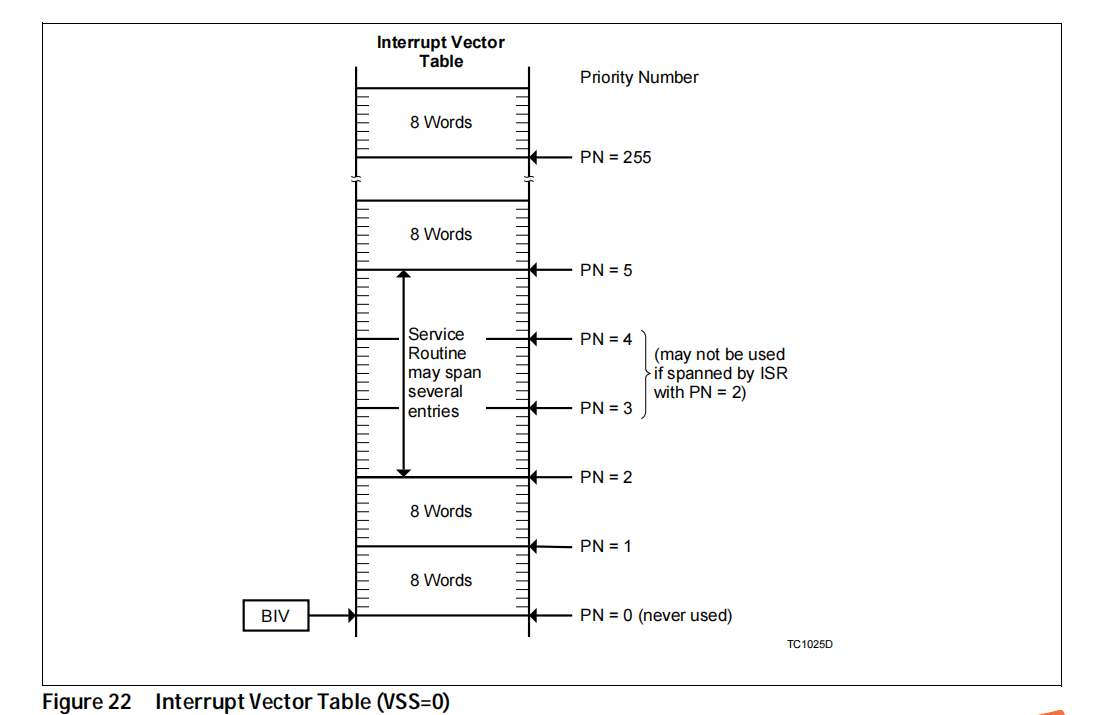

如果 中断处理程序 很短,它可能可以完全存储在对应的向量位置处(VSS=0时,每个向量占 32 字节)。此外,一个中断处理程序也可以跨多个向量条目(需要被占用的向量表位置,没有被其它中断使用)。

更通用的处理方式是,向量表中会包含一些 初始指令,随后再跳转到 完整处理程序 的位置。

BIV 寄存器允许 中断向量表 被定位在可用代码存储器的任何位置。上电后的默认值取决于具体实现。在 系统初始化阶段,在启用中断之前,可以使用 MTCR 指令写入 BIV 寄存器。此外,也可以使用多个 中断向量表,并且可以通过简单地修改 BIV 寄存器的内容在它们之间切换。

4 TriCore 中断系统的使用

TriCore 架构的灵活中断系统可用于解决常规和特殊的应用需求。

4.1 跨向量条目扩展中断服务程序(ISR)

由于向量条目与中断源无关,ISR 可以跨多个向量条目位置进行扩展,避免跳转操作。当 ISR 扩展时,占用的向量条目对应的优先级号不得分配给同一服务提供者的其他服务请求节点(SRN),如前文 图一 所示。

4.2 中断优先级组

中断优先级组定义了一组无法互相打断的中断服务程序。这种分组机制可以通过 TriCore 的中断系统架构轻松实现。

CPU 在处理中断时会禁用整个中断系统,并将当前 CPU 优先级(CCPN)设置为正在处理的中断的优先级,阻止所有低优先级的中断请求,直到中断系统重新启用或 ISR 通过 RFE 指令终止。 若在 ISR 中重新启用中断系统,但不改变 CCPN,则所有优先级低于或等于 CCPN 的中断仍无法执行。但具有更高优先级的中断可打断当前 ISR。

在一些应用场景中,多个重要的中断请求需要被分组,以确保同一组中的成员不会相互打断。可通过让 ISR 在启用中断系统前,将 CCPN 设为该组中最高的优先级编号,来实现此功能。 例如,编号 11 和 12 形成一组,而 14 到 17 形成另一组。每次处理 11 或 12 时,ISR 会将 CCPN 设为 12,每次处理 14 到 17 时,则设为 17,确保组内的中断不会相互打断。 此外,编号 13 可单独形成一组,或者将 CCPN 设为最大值 255,使所有中断被归入同一组,完全禁止中断嵌套。

4.3 将 ISR 划分为不同优先级

中断服务程序(ISR)可以很容易地分为具有不同优先级的部分。

例如,当某个中断的响应时间至关重要时,它可以被设置为极高的优先级,以确保关键任务立即执行,而后续的非关键任务可以在较低优先级运行。

因此,该服务程序被分为两部分:一部分执行关键任务,另一部分执行次要任务。 首先,中断节点的优先级被设置为较高优先级,使得当中断发生时,关键任务能够立刻执行。随后,该中断的优先级被降低,并且通过软件再次设置中断请求位(触发低优先级中断),高优先级服务程序结束后,返回到被中断的程序时。此时,如果 CPU 的优先级低于软件触发的 低优先级中断,挂起的低优先级中断会被处理。在此服务程序的新地址处,执行该中断的剩余低优先级任务。

在某些情况下,中断请求的优先级可能较低,因为对事件的响应时间并不紧急,但一旦开始服务,它不应被其他中断打断。为了防止中断过程被打断,TriCore 架构允许在 ISR 内提升服务请求的优先级,并允许完全禁用中断。

4.4 为同一中断源分配不同的优先级

在某些应用场景下,中断请求的优先级相较于其他请求并不是固定的,而是根据系统的当前状态动态调整。这可以通过在不同时间分配不同的 服务请求优先级编号(SRPN) 来实现,通常 ISR 也会依据其当前优先级执行不同的代码。 在传统的中断系统中,ISR 需要检查当前中断请求的优先级,并跳转到相应的代码段,这种方式会导致响应时间延迟。而在 TriCore 系统中,不同优先级的中断请求会自动有不同的向量条目,因此 ISR 无需额外检查和跳转,从而减少了中断延迟。

注意: 在创建 中断向量表 时,需要考虑为同一中断分配不同优先级的情况。

4.5 中断控制寄存器

两个 CSFR(核心特殊功能寄存器)支持中断处理:

ICR:存储当前 CPU 优先级编号(CCPN),中断系统启用/禁用位(IE),挂起中断优先级编号(PIPN),以及用于中断仲裁的特定实现控制项。

BIV:存储 中断向量表 的基地址。

ICR 中断控制寄存器,包含如下字段信息:

- PIPN [23:16]:待处理中断优先级编号。一个只读位字段,由 ICU(Interrupt

Control Unit)在每次中断仲裁过程结束时更新。表示待处理服务的优先级编号。当没有待处理请求时,以及每个新的中断仲裁过程的开始,PIPN 设置为 0。 - IE [15]:全局中断使能控制位。一个中断服务请求能被传送到 CPU, 需要对应的SRN 中的服务请求启用位(SRE)使能, 以及 这里的全局中断使能控制位被使能。

ICR.IE 在进入和退出 ISR 会自动更新。当进入中断 ISR 时 IE 位被清0,在 ISR 执行 RFE 时恢复为被中断前的值。ICR.IE 也可以通过

执行 ENABLE、DISABLE、MTCR 和 BISR 指令。

0 : 中断系统已全局禁用。

1 : 中断系统已全局启用。 - CCPN [7:0]:当前CPU优先级。该值会在进入/退出 ISR 时由硬件自动更新,或执行 BISR 指令时更新。也可以使用 MTCR 指令修改该值(注意使用ISYNC)。

BIV 中断向量表基地址寄存器,包含如下字段信息:

- BIV [31:1]:存储中断向量表基地址,该地址需要偶数对齐。

- VSS [0]: 中断向量表中每个条目的大小。

- 0:32个字节

- 1:8个字节